DDR4 PCB설계시 고려해야할 디자인 가이드에 대해서 알아보도록 하겠습니다.

내용은 DDR4 ECC SO-DIMM 기준으로 설명됩니다.

Design guide는 절대적인 값이 아니며 적층구조와 시스템 구성에 따라서 차이가 발생할수 있습니다.

우선, 임피던스 관리부터 알아보도록 하겠습니다.

1. 임피던스 관리

1) ECC SO-DIMM 2DPC

CLK Differential 88 ohm

CTRL,CKE Single 40 ohm

CMD Single 35 ohm

DQS Differential 75 ohm

DQ Single 42 ohm

ECC Single 42 ohm

Alert Single 35 ohm

Reset Single 50 ohm

RCOMP Microstrip 12~15mils width

1) ECC SO-DIMM 1DPC

CLK Differential 88 ohm

CTRL,CKE Single 40 ohm

CMD Single 40 ohm

DQS Differential 88 ohm

DQ Single 50 ohm

ECC Single 50 ohm

Alert Single 40 ohm

Reset Single 50 ohm

RCOMP Microstrip 12~15mils width

* 시스템의 구성과 적층구조를 충분히 고려하여 SI(Signal Integrity) 측면도 고려하여 임피던스를 매칭한다.

2. 배선의 길이 매칭 (Skew)

편의상 PCB설계에서 skew는 배선의 길이로 환산하여 관리한다.

CK 0과 1의 Length 차이는 40mils이내 배선

CK와 CK#의 차이는 +/- 5mil

CTRL/CLE는 차이는 200mils이내 배선 (CK와 같거나 100mils 이내로 짧을것)

CMD 끼리 차이는 200mls이내 (CK 보다 -500mil~+500mil)

DQS와 DQS#은 +/- 5mil (CK 보다 -1500mil~+2500mil)

DATA Group내 20mil 이내 차이

주) 이때 아래의 사항을 함께 고려한다.

1) CPU의 Package Length를 포함하여 관리한다.

2) Length Matching = CPU Die to SO-DIMM Pin (PKG + BO1 + BO2 + M + BI, PKG + BO1 +BO2a + BO2b + M

+ BI); where a conversion factor of 0.9 must be used on Micro-Strip Segments to convert Micro-Strip lengths

to Strip-Line equivalent lengths

3) Byte[0] = DQ[7:0], DQS/DQS#[0], Byte[1] = DQ[15:8], DQS/DQS#[1], Byte[2] = DQ[23:16], DQS/

DQS#[2], Byte[3] = DQ[31:24], DQS/DQS#[3], Byte[4] = DQ[39:32], DQS/DQS#[4], Byte[5] = DQ[47:40],

DQS/DQS#[5], Byte[6] = DQ[55:48], DQS/DQS#[6], Byte[7] = DQ[63:56], DQS/DQS#[7]

3. Vias separation

DQS,DQ,CLK,CTRL,CKE = 1 GND VIA 이상

시뮬레이션 결과에 따라서 VIA 간격은 조절한다.

30 mils 간격으로 배치한다.

4. VREF

VREF_DQ_A, VREF_DQ_B, VREF_CA는 20mils width에 20mils Space를 유지한다.

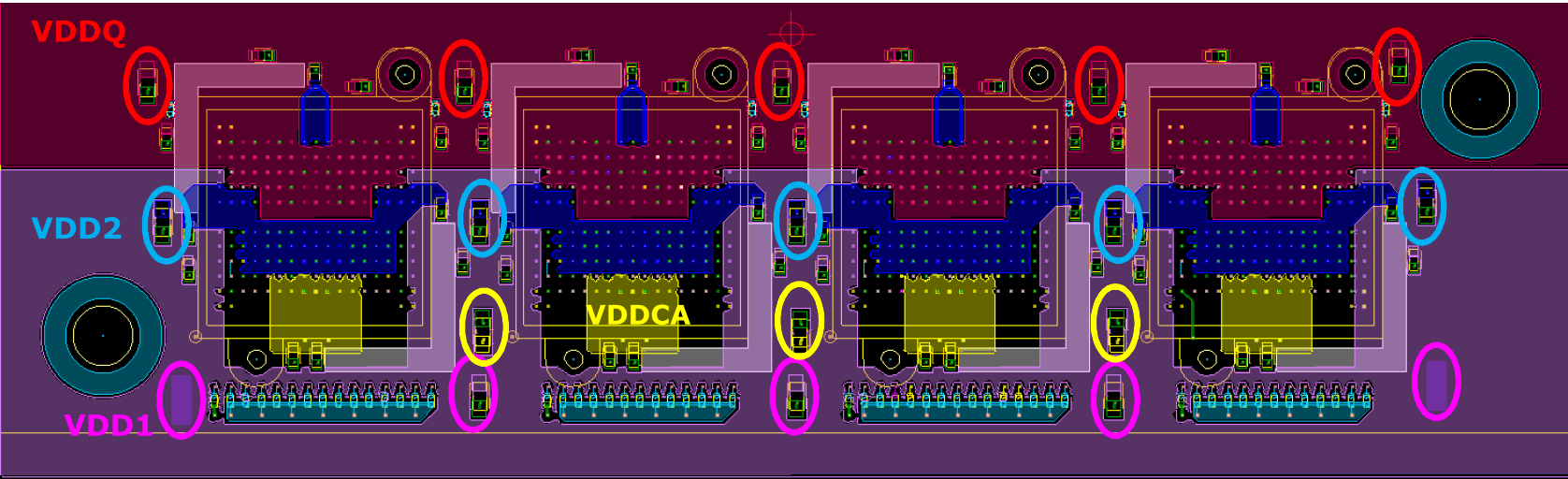

5. 디커플링 커패시터의 배치와 파워 배선

'[ PCB설계실무 ] > DDR4 Design' 카테고리의 다른 글

| [DDR4] 8세대 CPU+ DDR4 Impedance Control & MAX length (0) | 2019.08.16 |

|---|---|

| [DDR4] Singal Group, Total Trace Length (0) | 2019.08.16 |